Tóm tắt:

Gần đây xuất hiện nhiều tuyên bố rằng một số quốc gia có thể sản xuất chip tiến trình 2nm mà không cần sử dụng hệ thống quang khắc EUV (Extreme Ultraviolet Lithography). Nếu đúng, đây sẽ là một đột phá mang tính cách mạng, bởi EUV đang được xem là điều kiện tiên quyết để sản xuất chip dưới 5nm.

Bài viết này phân tích cơ sở khoa học của tuyên bố trên dưới góc nhìn của định luật Rayleigh, cấu trúc hệ thống quang học DUV/EUV, các công nghệ khắc thay thế (e-beam, nano-imprint, wet-lithography, photolithography với index cao), đồng thời đánh giá lại tương lai của định luật Moore – đặc biệt khi transistor tiến gần tới giới hạn vật lý cỡ nguyên tử.

Cuối cùng, bài viết đặt ra vấn đề chiến lược: Liệu Việt Nam có thể tham gia vào chuỗi giá trị chip tiên tiến, đặc biệt là giai đoạn lithography, transistor thế hệ mới và công nghệ đóng gói tiên tiến?

1. Giới thiệu

Lithography luôn là “trái tim” của ngành chế tạo bán dẫn. Khi tiến tới tiến trình 7nm – 5nm – 3nm và đặc biệt là 2nm, thế giới dựa gần như hoàn toàn vào công nghệ EUV của ASML (Hà Lan). Hệ thống EUV giá ~200–350 triệu USD/máy, vận hành cực kỳ phức tạp, duy nhất một hãng trên thế giới chế tạo.

Vậy làm chip 2nm không dùng EUV có khả thi hay không?

Để trả lời, cần quay lại nguyên lý vật lý cơ bản nhất của quang khắc.

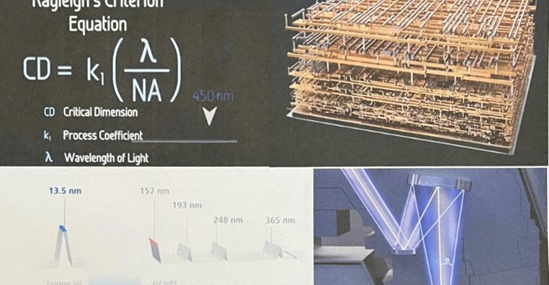

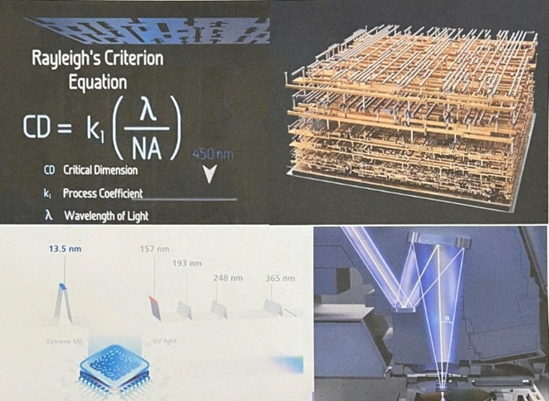

2. Cơ sở lý thuyết: Định luật Rayleigh và giới hạn của bước sóng

Độ phân giải nhỏ nhất mà hệ thống lithography có thể tạo ra được mô tả bởi phương trình Rayleigh:

Trong đó:

– CD – Critical Dimension: kích thước nhỏ nhất của đường mạch

– k₁ – hằng số công nghệ (thường ~0.25 – 0.4 đối với EUV)

– λ – bước sóng bức xạ

– NA – numerical aperture (khẩu độ số của hệ quang học)

Nguồn sáng hiện nay:

– DUV ArF: λ = 193 nm

– EUV: λ = 13.5 nm

Với λ = 193 nm, để đạt CD = 2 nm thì theo Rayleigh:

Đây là vô lý về vật lý, bởi:

– Để CD = 2 nm khi k₁ = 0.25 thì NA ≈ 24 – không tưởng về mặt thiết kế quang học (NA hiện nay ~0.33–0.55).

– Dù dùng kỹ thuật multiple patterning (N× patterning), giới hạn lý thuyết vẫn không thể “phá luật” Rayleigh.

Do đó, các hệ thống DUV không thể đạt 2nm nếu không có các kỹ thuật bổ trợ hoàn toàn mới hoặc phương pháp khắc phi quang học.

3. Có thể thay thế EUV bằng các công nghệ phi truyền thống không?

Có 4 hướng thay thế tiềm năng:

3.1. Electron-beam lithography (E-beam)

Ưu điểm:

– Độ phân giải rất cao (<1 nm)

– Không phụ thuộc bước sóng

Nhược điểm:

– Tốc độ cực chậm

– Không thể dùng cho sản xuất đại trà (mass production)

– Chi phí lớn

Kết luận: Có thể làm chip 2nm trên wafer mẫu (sample), nhưng không thể sản xuất hàng loạt.

3.2. Wet lithography với môi trường có chiết suất cao

Nếu môi trường có chiết suất (n) cao, bước sóng hiệu dụng sẽ giảm:

Giả sử n = 6–8 (lý thuyết cao nhất), λ = 193 nm:

Vẫn không đủ để đạt 2 nm.

Vấn đề lớn nhất:

– Không có vật liệu quang học thực tế có chiết suất n > 2 trong UV sâu.

– Không tồn tại hệ quang học hoàn chỉnh cho môi trường như vậy.

Kết luận: Không khả thi trong sản xuất thực tế.

3.3. Nano-imprint lithography (NIL)

Nhật Bản từng đi đầu trong công nghệ NIL.

Phương pháp này ép trực tiếp khuôn nanomet lên resist.

Ưu điểm:

– Độ phân giải cao

– Không cần EUV

– Thiết bị rẻ hơn rất nhiều so với EUV

Nhược điểm:

– Defect rate cao

– Khó canh chỉnh overlay

– Không phù hợp với tiến trình phức tạp đa lớp của chip logic tiên tiến

Kết luận: Có thể dùng cho vài lớp đơn giản; không thể thay thế toàn bộ EUV cho chip 2nm.

3.4. Advanced multiple patterning (Quad/Octo patterning)

Lý thuyết: dùng DUV 193 nm qua 6–8 lần patterning để đạt hiệu quả như EUV.

Nhược điểm:

– Yield thấp

– Chi phí khổng lồ

– Thiết kế mask phức tạp đến mức gần như “không tưởng”

– Điện trở – điện dung đường dây (RC delay) tăng mạnh

Kết luận: Đường mạch có thể xuống nhỏ, nhưng chip sẽ không thể hoạt động với hiệu năng mong muốn.

4. Định luật Moore đang chạm tới giới hạn vật lý

Khi transistor tiến tới kích thước cỡ nhỏ hơn 1 nm, vật lý lượng tử sẽ chi phối, dẫn tới:

– Tunnel effect tăng -> rò điện

– Không còn “cổng” điều khiển chính xác

– Tỉ lệ tỏa nhiệt tăng phi tuyến

– Tuổi thọ chip giảm

Do đó, transistor truyền thống (FinFET) sẽ phải chuyển sang:

– RibbonFET / Gate-all-around (GAAFET)

– CFET (stacked transistor)

– 3D logic stacking (monolithic 3D)

Đây là xu hướng bắt buộc khi thu nhỏ transistor không thể tiếp tục mãi theo Moore.

5. Nút thắt lớn nhất của chip tương lai: TẢN NHIỆT

Khi tăng mật độ transistor trên cùng một diện tích và tăng xử lý song song (parallel processing):

– Điện năng tiêu thụ tăng

– Nhiệt độ tăng cao

– Hiệu suất giảm mạnh khi quá nóng

– Tuổi thọ chip bị rút ngắn

Do đó, công nghệ tản nhiệt cấp độ chip (on-chip heat dissipation) trở thành “cổ chai” của ngành bán dẫn trong 20 năm tới.

Giải quyết được vấn đề tản nhiệt → chip AI quy mô lớn (tản nhiệt cho hàng ngàn nhân AI) mới trở thành hiện thực.

6. Đóng gói tiên tiến – Hướng đi khả thi thay cho EUV

Trong bối cảnh lithography chạm trần kỹ thuật, các tập đoàn lớn đang đầu tư vào:

– 2.5D/3D advanced packaging

– Chiplet architecture

– Hybrid bonding

– TSV, SoIC, CoWoS, Foveros

Advanced packaging có thể tăng hiệu năng gấp 3–10 lần mà không cần thu nhỏ transistor.

Do đó, có thể khẳng định: “Advanced packaging sẽ là giải pháp công nghệ cho nền công nghiệp bán dẫn trong tương lai.”

7. Vậy: Việt Nam có thể tham gia được phần nào?

Dựa trên phân tích khoa học ở trên, câu trả lời:

7.1. Việt Nam không thể làm chip 2nm đầy đủ trong 10–20 năm tới

Lý do:

– Không có EUV

– Không có industry ecosystem

– Không có vật liệu – thiết bị – nhân lực R&D đáp ứng

– Không có supply chain photomask, resist, gas, metrology

Đây là thực tế khách quan.

7.2. Nhưng Việt Nam có thể tham gia 3 hướng dưới đây:

(1) Advanced packaging – Hoàn toàn khả thi

– Không cần EUV

– Phù hợp năng lực doanh nghiệp Việt

– Nhu cầu toàn cầu tăng mạnh (chip AI, chiplet)

– Đang là “điểm yếu nhất” của thế giới → cơ hội lớn

(2) Thiết kế chip (fabless)

– Tận dụng nguồn nhân lực trẻ

– Không cần nhà máy

– Phù hợp chiến lược quốc gia

– Có thể làm chip AI, IoT, RF, analog

(3) Công nghệ Nano Plasma – vật liệu bán dẫn thế hệ mới

– Nano plasma

– Thin-film deposition

– Photonics

– LED materials

Đây là lĩnh vực Việt Nam có thể đi đường vòng khoa học, tạo công nghệ gốc.

8. Kết luận

Tuyên bố sản xuất chip 2nm mà không dùng EUV là không phù hợp với giới hạn vật lý của quang học hiện đại, trừ phi có một đột phá hoàn toàn mới về lithography hoặc vật liệu lượng tử.

Trong bối cảnh thế giới bước vào kỷ nguyên hậu-Moore:

– Tản nhiệt trở thành vấn đề lớn nhất

– Đóng gói tiên tiến trở thành chìa khóa

– Chiplet trở thành chuẩn mới

– Transistor tiến tới giới hạn nguyên tử

Việt Nam không thể chạy đua lithography, nhưng có thể chọn chiến lược thông minh:

– Thiết kế chip

– Đóng gói tiên tiến

– Vật liệu nano plasma

– R&D vật liệu mới

– Công nghệ tản nhiệt

– Đào tạo nhân lực bán dẫn Điều quan trọng nhất là xây dựng hệ sinh thái nghiên cứu – đào tạo – doanh nghiệp.