1. Giới thiệu

Trong hơn năm thập kỷ, ngành công nghiệp bán dẫn vận hành theo định luật Moore, dẫn đến quá trình thu nhỏ liên tục từ các chip 3 µm (1980s) xuống 1.6 nm (2025). Tiến trình thu nhỏ này không chỉ phản ánh khả năng điều khiển vật liệu ở thang kích thước nguyên tử, mà còn thể hiện sự cạnh tranh công nghệ giữa các quốc gia và tập đoàn lớn nhất thế giới.

Bài viết mở rộng phân tích gốc của GS. Từ Trung Chấn, đưa thêm dòng thời gian công nghệ, xu hướng thu nhỏ 3 thập niên qua, cùng với các bước tiến mới nhất của TSMC và Intel. Bài viết cũng làm rõ vì sao, mặc dù sở hữu công nghệ 1.8 nm, Intel vẫn thất bại trong thương mại hóa do chậm đầu tư vào hệ thống EUV – một quyết định chiến lược ảnh hưởng trực tiếp đến giá cổ phiếu và vị thế cạnh tranh của tập đoàn.

2. Dòng thời gian thu nhỏ kích thước công nghệ bán dẫn (1980–2022)

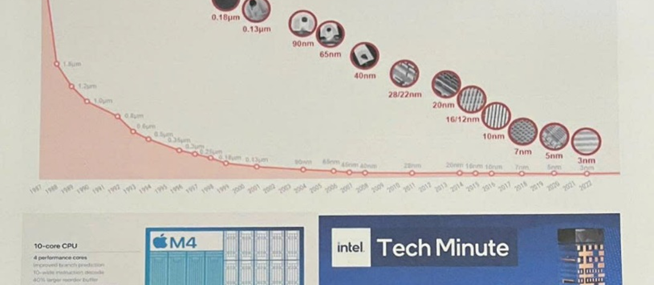

Hãy quan sát hình minh họa sau:

Có thể thấy tiến trình giảm kích thước từ 3 µm → 3 nm theo biểu đồ logarit. Dưới đây mô tả chuẩn hóa thành dòng thời gian công nghệ từ 3 µm → 3 nm:

| Năm | Thế hệ tiến trình | Mốc công nghệ nổi bật |

| 1980–1985 | 3 µm → 1.5 µm | CMOS thế hệ đầu, transitor hàng trăm ngàn |

| 1990 | 1.2 µm → 0.8 µm | Bắt đầu chuẩn hóa photolithography DUV |

| 1995 | 0.5 µm → 0.35 µm | Tối ưu doping, interconnect bằng nhôm |

| 1999 | 0.25 µm → 0.18 µm | Bắt đầu giảm RC-delay, dùng đồng (Cu) |

| 2003 | 130 nm | Thế hệ Intel Pentium, TSMC G1 |

| 2005–2006 | 90 nm → 65 nm | Chuyển sang vật liệu low-k dielectric |

| 2009 | 45 nm → 32 nm | HKMG – High-k Metal Gate |

| 2012 | 28 nm | GPU/CPU thế hệ ARM bùng nổ |

| 2014 | 22 nm → 16/14 nm | FinFET xuất hiện, siêu tiết kiệm năng lượng |

| 2018 | 10 nm → 7 nm | EUV bắt đầu được dùng hạn chế |

| 2020 | 5 nm | Apple A14, TSMC N5 |

| 2022 | 3 nm | TSMC N3 – thế hệ GAAFET |

Biểu đồ và bảng trên cho thấy:

– Mỗi thế hệ mới giảm ~20–30% kích thước transistor.

– Sau dưới 10 nm, mọi bước nhảy đều phụ thuộc EUV.

3. Bổ sung phân tích về tiến trình 2023–2025

3.1. TSMC – 2 nm sản xuất năm 2023

TSMC đã chính thức đưa vào sản xuất quy trình N2 vào cuối 2023:

– sử dụng EUV thế hệ thường (0.33 NA) nhưng patterning tối ưu

– GAAFET thương mại hóa

– giảm ~15% điện năng, tăng ~10–15% hiệu năng so với 3 nm

Điểm quan trọng: TSMC có đầy đủ EUV từ 2020, nên 2 nm trở thành bước tiếp theo tất yếu.

3.2. Intel – 1.8 nm (Intel 18A) năm 2024

Intel công bố tiến trình 1.8 nm (18A) với hai công nghệ đột phá:

– RibbonFET – transistor dạng ribbon

– PowerVia – cấp nguồn điện từ đáy chip

Trên lý thuyết, Intel 18A có thể vượt TSMC 2 nm, nhưng chỉ ở mức:

– công bố kỹ thuật

– thử nghiệm giới hạn

Không được thương mại hóa hàng loạt, nguyên nhân sẽ được phân tích ở phần 5.

3.3. TSMC – 1.6 nm năm 2025

Đầu 2025, TSMC công bố tiến trình 1.6 nm:

– Sử dụng EUV High-NA thế hệ mới

– Độ phân giải bước sóng ~8–10 nm

– Patterning giảm từ 4–6 bước xuống 1–2 bước

TSMC chính thức bước vào giai đoạn hậu-Moore, nơi thu nhỏ transistor gần tới mức 5–8 lớp nguyên tử.

4. Tại sao thu nhỏ transistor trở nên cực kỳ khó?

Dựa trên phân tích trong file gốc , các giới hạn vật lý trở nên rõ ràng:

4.1. Giới hạn quang học (Rayleigh)

Không thể có lithography dưới 2 nm với bước sóng 193 nm của DUV.

4.2. Giới hạn lượng tử

Khi transistor nhỏ hơn 1 nm:

– electron xuyên hầm (quantum tunneling)

– không thể điều khiển dòng chính xác

– transistor mất khả năng đóng – mở

4.3. Tản nhiệt (heat dissipation)

Đây là “cổ chai” lớn nhất của chip AI:

– mật độ transistor tăng

– năng lượng tiêu tán theo nhiệt tăng

– hiệu suất giảm

– tuổi thọ chip giảm mạnh nếu không có vật liệu tản nhiệt mới

Điều này khiến các hãng như NVIDIA, AMD, Apple tập trung nhiều hơn vào đóng gói tiên tiến và chiplet, thay vì tiếp tục thu nhỏ transistor vô hạn.

5. Intel: Bài học chiến lược từ việc không đầu tư EUV đúng thời điểm

Đây là điểm quan trọng nhất cần nhấn mạnh theo yêu cầu của bạn.

5.1. Sự chậm trễ mang tính lịch sử

Trong giai đoạn 2015–2020:

– Intel không mua EUV của ASML

– TSMC và Samsung mua hàng trăm máy EUV

– Điều này dẫn đến:

| Năm | TSMC | Intel |

| 2018 | 7 nm (EUV-ready) | 10 nm gặp lỗi |

| 2020 | 5 nm thương mại | 7 nm chậm 3 năm |

| 2023 | 2 nm | chưa có EUV đủ để mass-produce |

Intel đã chính thức bỏ lỡ 2 thế hệ công nghệ liên tiếp.

5.2. Hệ quả trực tiếp: Intel 18A không thể thương mại hóa

Dù Intel 18A (1.8 nm) là một tiến bộ kỹ thuật lớn, nhưng:

– không đủ EUV → không thể sản xuất hàng loạt

– yield không ổn định

– chi phí patterning quá cao

– không thể giao chip đúng lộ trình

Kết quả:

→ Intel không thể bán chip 18A ra thị trường.

→ TSMC tiếp tục thống trị toàn cầu ở 5 nm – 3 nm – 2 nm.

5.3. Hệ quả tài chính: giá cổ phiếu giảm mạnh

Các nhà phân tích Phố Wall đã nêu rõ:

– Intel công bố đột phá khoa học → có

– Intel không thể sản xuất thương mại → không thể thu lợi nhuận

Điều này khiến:

– niềm tin nhà đầu tư giảm

– cổ phiếu Intel giảm liên tục từ 2021–2024

– giá trị thị trường của Intel thấp hơn NVIDIA, TSMC và thậm chí thấp hơn AMD

Đây là bài học chiến lược quan trọng:

Không đầu tư đúng thời điểm vào thiết bị cốt lõi (EUV) → mất toàn bộ thị trường.

6. Tác động đối với ngành bán dẫn Việt Nam

Việt Nam cần nhận thức rõ:

6.1. Không thể cạnh tranh ở lithography tiên tiến

Vì:

– Chi phí EUV quá lớn

– Chuỗi cung ứng vật liệu – thiết bị không tồn tại

– Không có nền công nghệ 40 năm tích lũy như TSMC hoặc Intel

6.2. Nhưng có thể cạnh tranh ở 3 hướng:

(1) Advanced packaging – hướng đi khả thi nhất

Việt Nam hoàn toàn có thể xây dựng nhà máy đóng gói 2.5D/3D.

(2) Thiết kế chip (fabless)

Không cần EUV, phù hợp nhân lực Việt Nam.

(3) Công nghệ vật liệu mới / Nano Plasma

Đây là lĩnh vực Việt Nam có thể đi đường tắt công nghệ.

7. Kết luận

Do đó, có thể kết luận:

1. Thu nhỏ tiến trình đang chạm tới giới hạn vật lý.

2. EUV là điều kiện tiên quyết – không có đường vòng.

3. TSMC dẫn đầu vì đầu tư EUV đúng thời điểm.

4. Intel tụt lại vì không đầu tư EUV kịp, dù kỹ thuật transistor rất tiên tiến.

5. Việt Nam cần tập trung vào thiết kế, đóng gói tiên tiến và vật liệu bán dẫn.